About¶

What is VHDL?¶

VHDL is an acronym for Verification and Hardware Description Language (HDL), which is a computer language used to describe a logic circuit by function, data flow behavior, or structure.

Note

Historically the ‘V’ in the language’s acronym came from the Very High Speed Integrated Circuit (VHSIC), which was the U.S. government program that funded the early work on the standard. Changing the ‘V’ to mean verification reflects the language’s increasing usage for verification as well as design. See VHDL 202X PAR via VHDL-202X.

Although VHDL was not designed for writing general purpose programs, VHDL is a programming language: any algorithm can be written with it, it can interact with files, the environment, stdin and stdout, etc. VHDL has features similar to those found in procedural languages such as C, Python, or Ada. Indeed, VHDL derives most of its syntax and semantics from Ada. Knowing Ada is an advantage for learning VHDL (it is an advantage in general as well).

However, VHDL was not designed as a general purpose language but as an HDL. As the name implies, VHDL aims at modeling or documenting electronics systems. Due to the nature of hardware components –which are always running–, VHDL is a highly concurrent language, built upon an event-driven execution model.

Like a program written in any other language, a VHDL program can be executed. Since VHDL is used to model designs, the term simulation is often used instead of execution, with the same meaning. At the same time, like a design written in another HDL, a set of VHDL sources can be transformed with a synthesis tool into a netlist, that is, a detailed gate-level implementation.

The development of VHDL started in 1983 and the standard is named IEEE 1076. Five revisions exist: 1987, 1993, 2002, 2008 and 2019. The standardization is handled by the IEEE P1076 Working Group: VHDL Analysis and Standardization Group (VASG). Find on-going work towards VHDL 202X in gitlab.com/IEEE-P1076/VHDL-Issues.

What is GHDL?¶

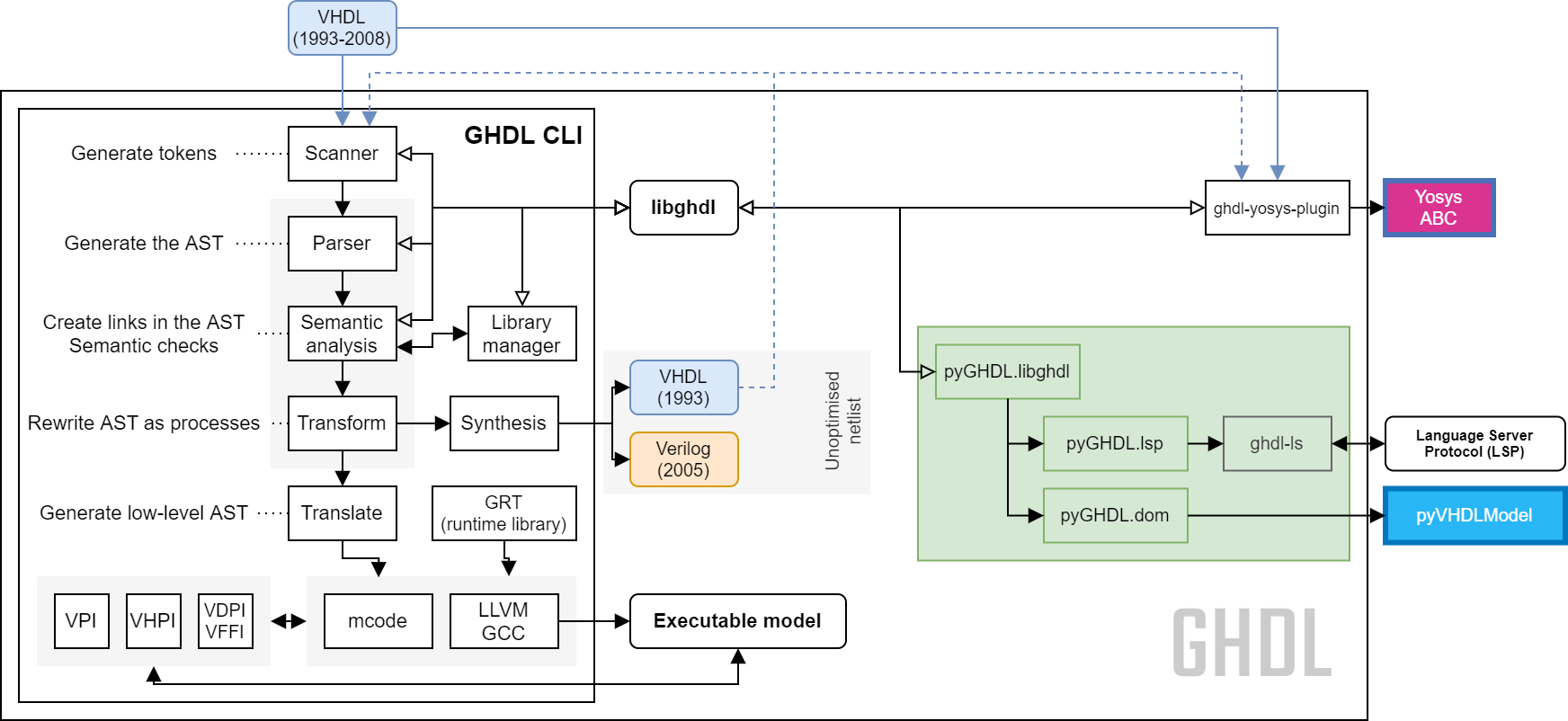

Architecture overview of the GHDL toolkit (CLI, libghdl, pyGHDL and ghdl-yosys-plugin).¶

GHDL is a shorthand for G Hardware Design Language (currently, G has no meaning). It is a VHDL analyzer, compiler, simulator and (experimental) synthesizer that can process (nearly) any VHDL design.

Note

For almost 20 years, GHDL was not a synthesis tool: a netlist could not be created. Hence, most of the content in this documentation corresponds to the usage of GHDL as a compiler/simulator. See Synthesis for further details regarding synthesis.

Unlike some other simulators, GHDL is a compiler: it directly translates a VHDL file to machine code, without using an intermediary language such as C or C++. Therefore, the compiled code should be faster and the analysis time should be shorter than with a compiler using an intermediary language.

GHDL can use multiple back-ends, i.e. code generators, (GCC, LLVM or x86/i386 only, a built-in one named mcode) and runs on GNU/Linux, Windows ™ and macOS ™; on x86, x86_64, armv6/armv7/aarch32/aarch64, ppc64, etc.

The current version of GHDL does not contain any built-in graphical viewer: signal waves cannot be seen through GHDL. However, the behavior of the designs can still be checked through test benches and verification frameworks. Moreover, GHDL Waveform (GHW), VCD or FST files can be produced, which can be viewed with an external waveform viewer, such as GtkWave.

GHDL aims at implementing VHDL as defined by IEEE 1076. It supports the 1987, 1993 and 2002 revisions and, partially, 2008 and 2019. Property Specification Language (PSL) is also partially supported.

Several third party projects are supported: Yosys (through the ghdl-yosys-plugin) cocotb, (through the VPI interface), VUnit, OSVVM, The pyVHDLModel Documentation, …

Who uses GHDL?¶

Project hub |

Documentation |

Name |

Brief description |

|---|---|---|---|

A Vendor-Independent, Open-Source IP Core and Utility Library. |

|||

A unit testing framework for VHDL/SystemVerilog |

|||

IEEE P1076 Working Group [VASG] |

|||

TTA-Based Co-Design Environment - an open-source ASIP toolset. |